一 .滤波器介绍

滤波器是一种用来减少,消除干扰的电器部件,有对特定频率的频点或该频点以外的频率信号进行有效滤除,从而实现消除干扰、获取特定频率信号的功能。数字滤波器相比模拟滤波器,有着更高的精度、信噪比、无可比拟的可靠性。

FIR,IIR是数字滤波器中最常见的两种滤波器。 FIR滤波器是有限冲击响应,最主要特点是没有反馈回路,故不存在不稳定的问题,很容易做到严格的线性相位特性,另外设计方式是线性的,硬件容易实现,对于抽取和插入,结构简单,很容易得到高速流水线的设计,有定义明确的量化噪声,并且有较低的系数和算法四舍五入误差预算,但是其高滤波器长度的实现需要大量的工作量及资源;IIR滤波器是无限冲击响应,最主要的特点是可以用较低的阶数,获得高的选择性,所用的存储单元少,计算量小,效率高。但是这样的效率是以非线性相位为代价的,选择性越好,相位非线性越严重。本文以FIR为例介绍数字滤波器的设计及验证。

二.FIR滤波器设计

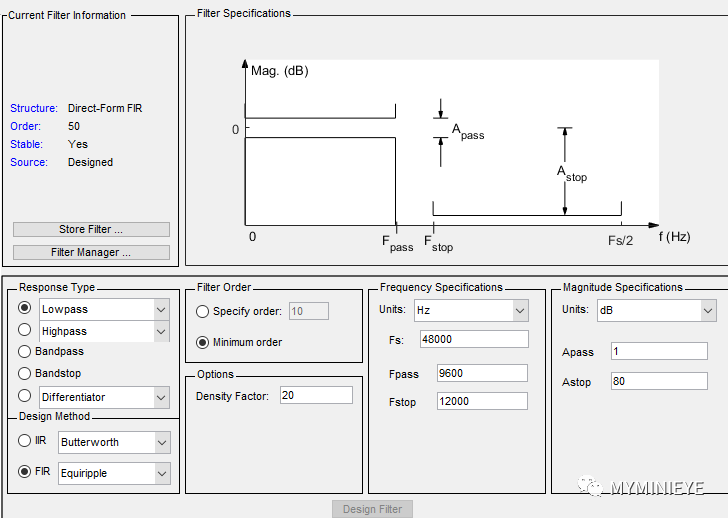

采用matlab的Filter Design 来完成对FIR滤波器的设计,打开matlab,在命令行输入filterDesigner,进入到设计页面,如下

对滤波器的设计主要涉及三个点:通带,阻带,过渡带。

主要的参数有以下5个:

Fpass:通带上限截至频率,Apass:带内平坦度;

Fstop:阻带下限截至频率,Astop:带外抑制幅度;

Fs:数据率

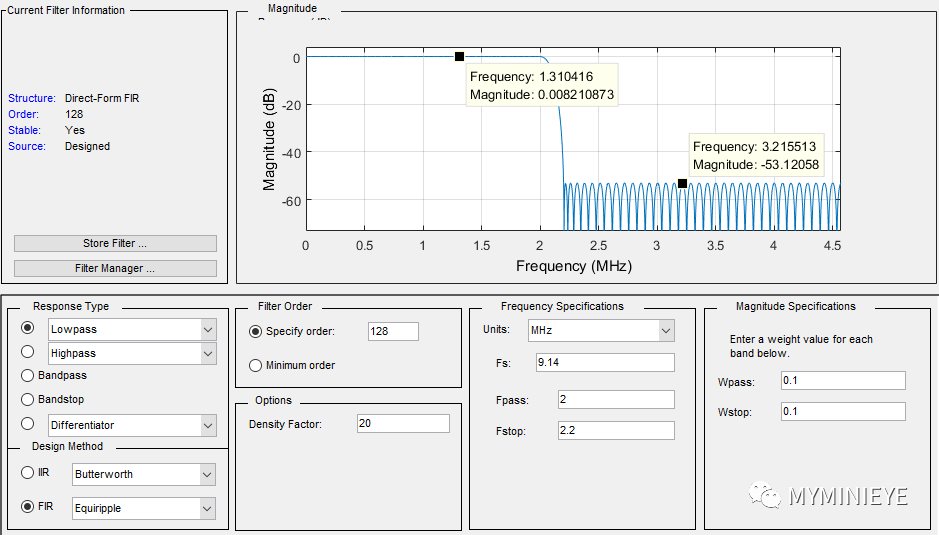

输入数据的速率为9.14MHz,通带上限截止频率为2M,由于考虑到镜像干扰,阻带截至频率设为2.2M,阶数选择128阶,滤波器阶数可以根据需要设置,也可以设置带内平坦度和带外抑制幅度,来选择所需最小阶数,达到自己需要的精度即可。设置完成之后,如下:

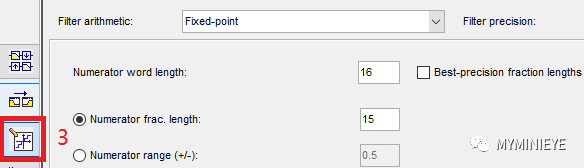

滤波器设计完成之后需要对滤波器的系数进行定点量化,选择按钮3,定义16位的数据位宽,其中15位为小数。如下:

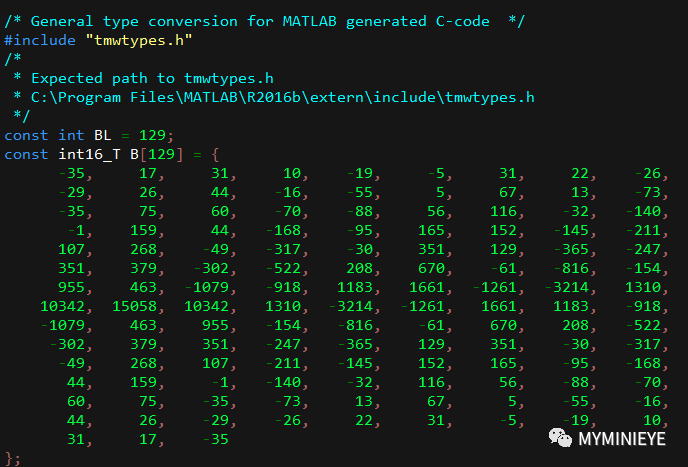

点击Filter Design菜单栏的Targets选项下拉菜单的Generate C Header和XILINX Coefficient(.COE) File,分别导出的是C的头文件和.coe文件(滤波器系数文件),C的头文件如下

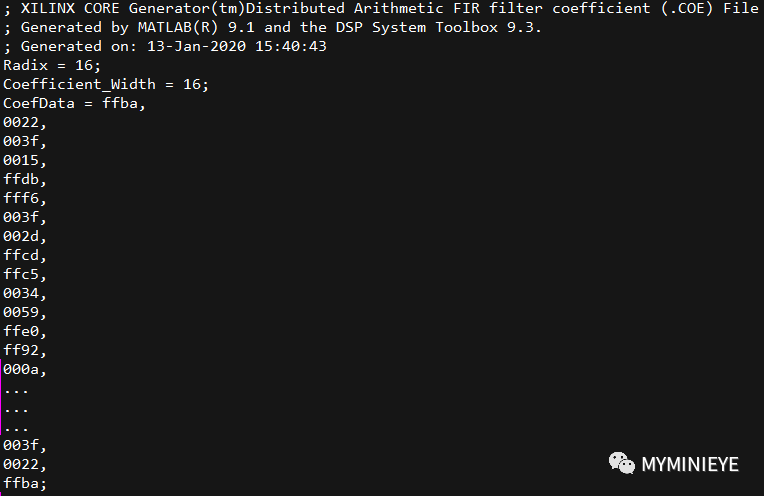

Coe文件为:

这里选择产生Generate C Header,产生滤波器系数,此处没有选择coe文件,是因为当vivado IP核使用coe方式导入时,vivado不能区分小数位。

三.vivado FIR IP核介绍

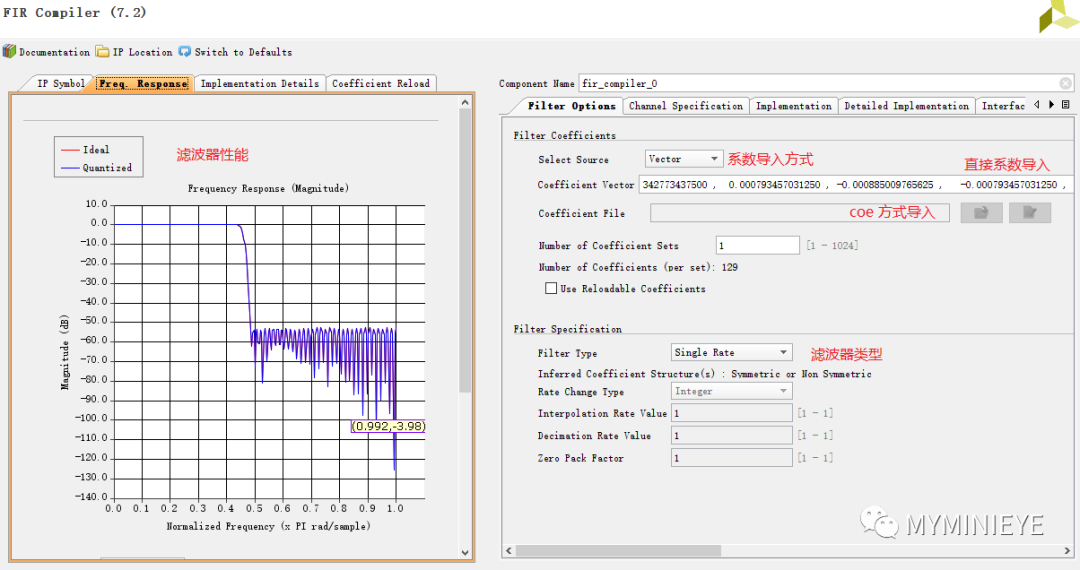

1.设置滤波器的属性 :打开vivado IP核,直接填入滤波器的系数,此处系数需要量化为小数,左边为滤波器的增益,和matlab一致,如下:

滤波器的类型包括单速率(Single Rate,即数据输出与输入速率相同),抽取(Decimation)和插值(Interpolation)应用于多速率信号处理系统,此外还支持希尔伯特变换(Hilbert)模式。抽取型一般多用于数字前端下变频抽取样值降低AD采样速率,插值型用于常用于提高采样速率。由于需要对AD数据进行抽取滤波,这里选择抽取类型,抽取的倍数为2倍。

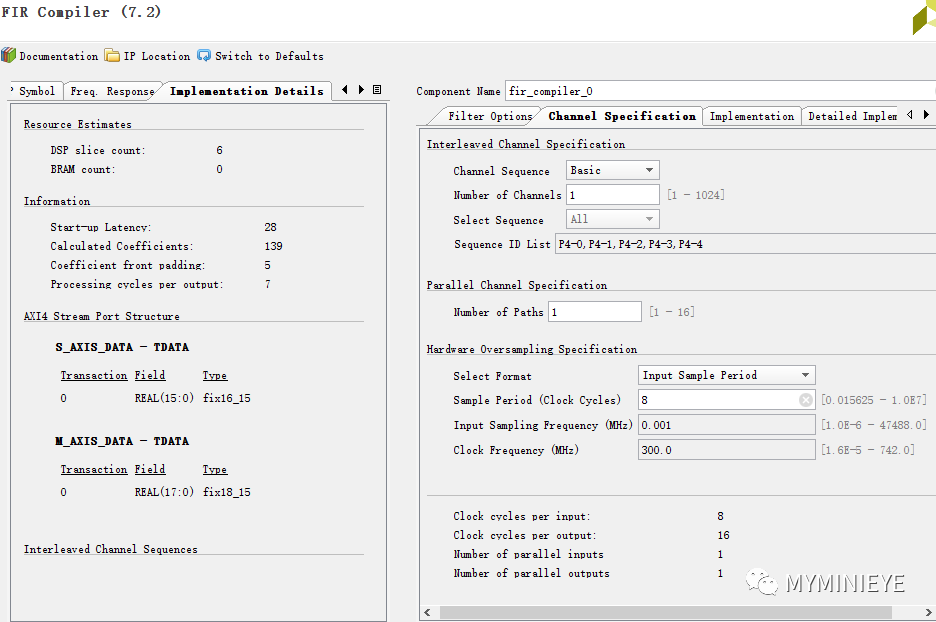

2.设置FIR滤波器的通道 ,由于只使用一个通道,因此交织通道序列(Channel Sequence)选择Basic,通道数(Number of Channels)为1;Hardware Oversampling Specification中设置过采样模式,选择Input Sample Period,即输入采样周期,也可以通过输入采样频率和时钟频率来设置,设置如下:

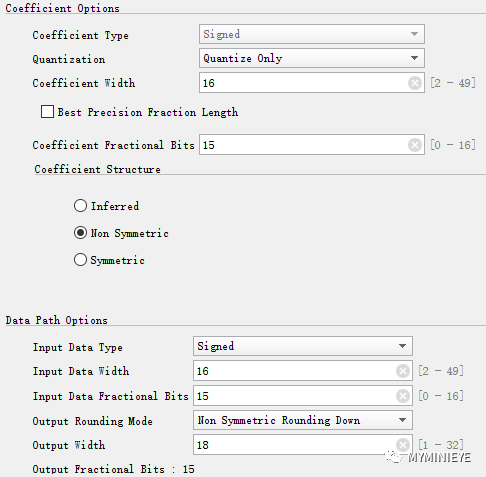

3.滤波器量化设置

填入滤波器系数之后,选择量化的位数,输入的数据位宽为16,小数位数为15,如果全精度输出,输出位宽为33,对后续的处理很不方便,输出也需要进行相应的截尾,因此设置为:

4.FIR滤波器在FPGA上实现资源选取的情况,一般采用系统默认即可。

5.对外输入和对外输入接口情况, 这里只添加复位信号,可以根据自己的实际需求,添加信号。

6.Summary是对FIR滤波器设计的总结,所使用的类型功能,滤波器阶数等,最后点击生成FIR IP核。

四.FIR 滤波器实现

1.C模型使用

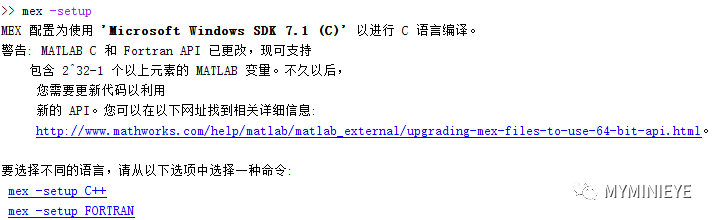

Vivado提供了FIR IP核的C仿真模型,但是不能直接再matlab上运行,需要搭建仿真环境,根据自己使用的matlab选择不同的版本。搭建完成之后在matlab命令窗口输入mex-setup,出现以下提示表示安装成功

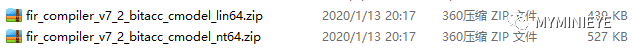

然后找到IP核C模型,在vivado工程FIR IP核的目录下的cmodel的文件夹,FIR_demo.srcs\\sources_1\\ip\\fir_compiler_0\\cmodel,其中有两个文件,lin64是linux版本的,nt64是windows版本的,选择nt64解压。

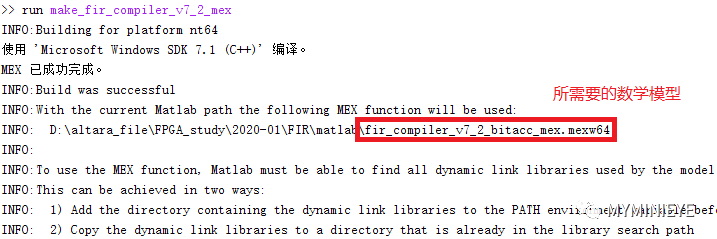

matlab打开解压的文件夹,输入run make_fir_compiler_v7_2_mex,出现以下表示运行成功。

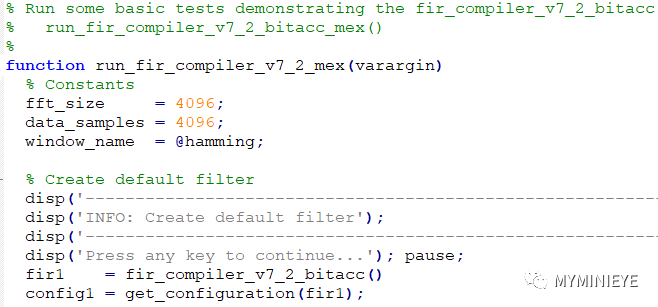

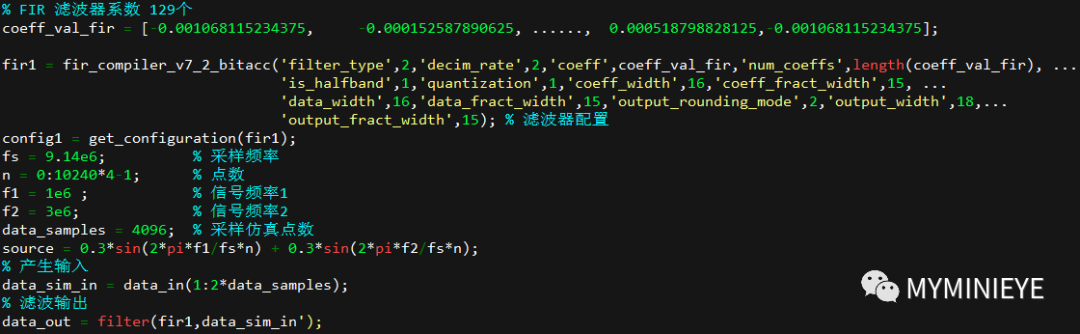

最后要调用的文件是run_fir_compiler_v7_2_mex.m,这个文件可以作为参考使用,部分内容为:

作如下修改:

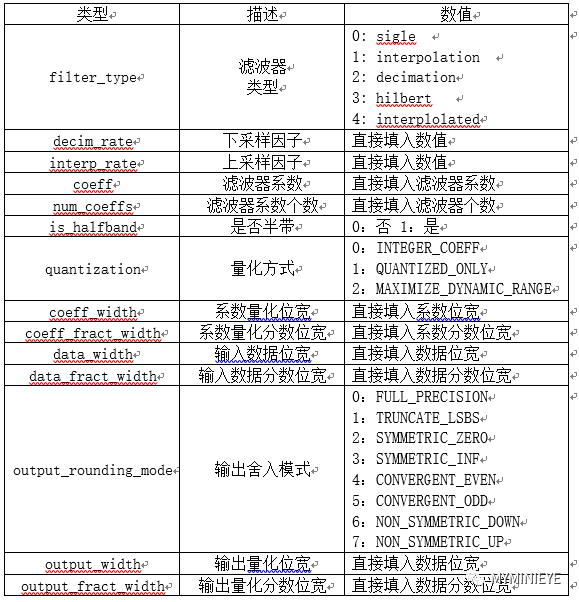

其中FIR参数设置要和vivado中的IP核配置完全相同,否则会出现比对数据不一致的情况,具体参数配置见下表

各类型对应的数值选择

2.Modelsim 仿真

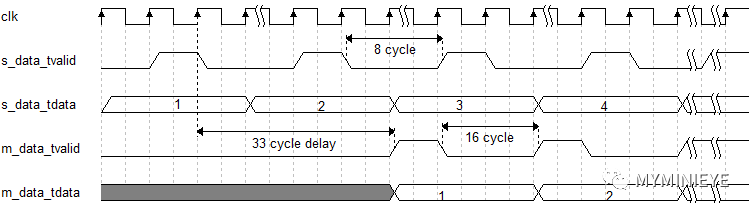

仿真时需要注意,采用的抽取类型,数据速率和时钟速率不一样,每隔8个时钟周期采一个数据,然后输入到FIR IP核,输出是每隔16个时钟周期输出一个数据,输出延迟可在FIR IP核Summary界面得知,模块时序如下:

3.数据对比

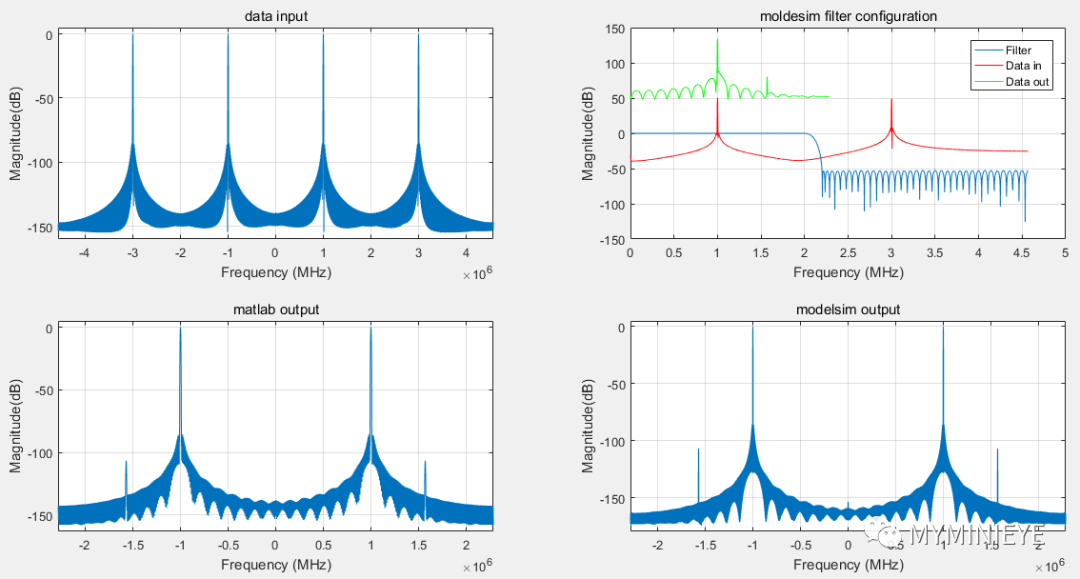

滤波器的截至频率为2MHz,用matlab产生一个1MHz和3MHz的混合信号,分别输入C仿真模型和modelsim进行仿真,得到的结果进行对比如下:

可以清楚的看到输出的结果是一致的,通过比较matlab和modelsim输出的数据,发现也是一致的,相减之后为零,验证了滤波器的正确性。